# **AN4616**

# **Driving Microchip SiC MOSFETs**

Author: Xuning Zhang, Dennis Meyer and Kevin

Speer

Microchip Technology Inc.

#### **PURPOSE**

This application note provides design guidance for properly selecting gate-source voltages for Microchip's SiC MOSFET products, along with related device performance and behavior.

This note applies to Microchip part numbers of the type MSCXXXSMAXXX.

# SPECIFYING GATE DRIVE VOLTAGES FOR SIC MOSFETS

The way gate drive voltages are specified on data sheets varies by manufacturer, but most will have some form of Table 1. We begin by defining some terms:

- V<sub>GS</sub> is the applied voltage between the MOSFET's gate and source terminals.

- V<sub>GSon</sub> is the steady-state V<sub>GS</sub> applied to turn the MOSFET on.

- V<sub>GSoff</sub> is the steady-state V<sub>GS</sub> applied to turn the MOSFET off.

- V<sub>GSmax</sub> is the manufacturer's maximum allowed steady-state V<sub>GS</sub>, shown for both negative and positive extremes.

- V<sub>GS,OP</sub> is the manufacturer's recommended steady state values for V<sub>GSon</sub> and V<sub>GSoff</sub>.

Some data sheets do not specify  $V_{GSon}$  and  $V_{GSoff}$ ; similar to silicon MOSFETs, different applications may call for different optimal values.

## MICROCHIP RECOMMENDATIONS

For optimal device performance and system stability, Microchip SiC MOSFETs are best driven using  $V_{GSon}$  = +20V and  $V_{GSoff}$  = -5V. Microchip SiC MOSFETs still perform well at lower absolute values of

$V_{GSon}$  and  $V_{GSoff}$ , but as with any design, the additional losses associated with sub-optimal drive conditions should be analyzed and understood. To this end, the reasoning behind optimal  $V_{GSon}$  and  $V_{GSoff}$  are different, and the expected trade-offs for each case are described in the following sections.

# ON STATE GATE DRIVE VOLTAGE, V<sub>GSon</sub>

Driving Microchip SiC MOSFETs with a lower V<sub>GSon</sub> will exhibit:

- Increased on-state resistance, resulting in higher conduction loss

- Reduced peak (saturation) current capability

- · Longer short circuit withstand time

- · Extended gate oxide lifetime

- Increased switching loss under the same gate resistance.

## On State Resistance, R<sub>DSon</sub>

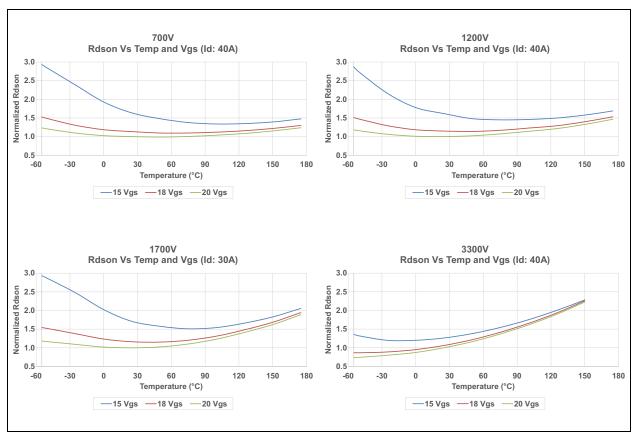

The four curves in Figure 1 show how the normalized  $R_{DSon}$  (normalized to  $R_{DSon}$  at 25°C and 20V gate voltage) increases with junction temperature,  $T_j$ . Data is shown for Microchip's largest SiC MOSFET die at each of four voltage classes: 700V, 15 m $\Omega$ ; 1200V, 17 m $\Omega$ ; 1700V, 35 m $\Omega$ ; and 3300V, 25 m $\Omega$ .

Some general observations include:

- The increase of R<sub>DSon</sub> for SiC MOSFETs with temperature is much lower than that of silicon MOSFETs.

- Microchip SiC MOSFETs show a lower increase of R<sub>DSon</sub> at elevated T<sub>j</sub> than other SiC MOSFET suppliers.

- At V<sub>GSon</sub> = 18V, R<sub>DSon</sub> shows a minor shift which gets even smaller at higher T<sub>i</sub>.

- At V<sub>GSon</sub> = 15V, the increase of R<sub>DSon</sub> is more substantial, particularly at lower T<sub>i</sub>.

TABLE 1: GATE SOURCE VOLTAGE SPECIFICATION

| Characteristics     | Symbol             | Conditions                      | Value     | Unit |

|---------------------|--------------------|---------------------------------|-----------|------|

| Gate-Source Voltage | V <sub>GSmax</sub> | Absolute maximum DC values      | -10 to 23 | V    |

|                     | $V_{GS,OP}$        | Recommended DC operating values | -5 to 20  | V    |

**FIGURE 1:** Temperature Dependency of R<sub>DSon</sub> Under Different Gate Voltage of Different Voltage Families.

# Designing for V<sub>GSon</sub> < 20V

Due to SiC's wide band gap, a higher electric field is required to invert the semiconductor of a MOS-gated transistor than is required for silicon. The electric field can be increased either by raising the applied  $V_{\rm GSon}$  or by reducing the thickness of the gate oxide. Raising  $V_{\rm GSon}$  may call for a new gate driver design, while reducing the oxide thickness could make the device more susceptible to failure. A third way to get more current is to increase die size, but this increases cost. Clearly the best technical and commercial choice is a new gate driver design, but what compromises are made if the ideal  $V_{\rm GSon}$  = 20V is impossible to achieve?

# EFFECT ON R<sub>DSon</sub>

When driving at lower values of  $V_{GSon}$ , designers should analyze how  $R_{DSon}$  changes across the junction temperature range of interest. If the  $R_{DSon}$  across relevant  $T_j$  is consistently within a close range of the  $R_{DSon}$  at  $V_{GSon}$  = 20V, the final design can accommodate these small differences and be extremely robust. For Microchip SiC MOSFETs, production measurement of  $R_{DSon}$  shows  $V_{GSon}$  = 20V is an excellent predictor of  $R_{DSon}$  at  $V_{GSon}$  = 18V; in the case of a 1200V SiC MOSFET at  $T_j$  = 175°C,  $R_{DSon}$  at  $V_{GS}$  = 18V is only 4% higher than  $R_{DSon}$  at  $V_{GS}$  = 20V.

In contrast, the comparison of  $R_{DSon}$  at  $V_{GSon}$  = 20V and  $V_{GSon}$  = 15V requires careful consideration. The variance is approximately 4x higher for  $V_{GSon}$  = 15V and dependent upon device threshold voltage,  $V_{GS(th)}$ . For this reason, Microchip does not recommend driving SiC MOSFETs of type MSCXXXSMAXXX at  $V_{GSon}$  = 15V. If they must be driven with 15V, a sufficient design margin for  $R_{DSon}$  should be considered. Contact your local Microchip sales office for support.

#### PARALLEL-CONNECTED SIC MOSFETS

There is a final point to be made about parallel-connected SiC MOSFETs and  $V_{GSon} < 20V$ . One can observe from the charts that the temperature coefficient of  $R_{DSon}$  may not be positive across the entire range of relevant  $T_j$ . In an extreme example, consider the 700V SiC MOSFET at  $V_{GSon} = 15V$ . This gate drive situation results in a SiC MOSFET with a negative temperature coefficient up to  $T_j = 80\text{-}100^{\circ}\text{C}$ . Ensuring that paralleled devices will evenly share current is a risk against which the design should be safeguarded. However, much as in the previous paragraphs, using  $V_{GSon} = 18V$  is the simplest solution and is well-suited for most applications.

# PEAK CURRENT CAPABILITY

When driving with a lower  $V_{GSon}$ , the MOSFET channel is not fully enhanced, and the maximum current is reduced.

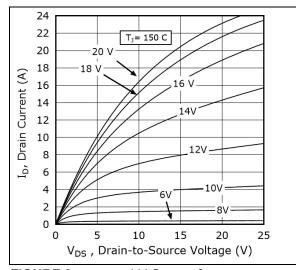

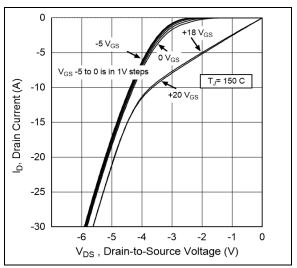

**FIGURE 2:** I-V Curve of MSC360SMA120B Under Different Driving Voltages at  $T_i = 150$ °C.

Figure 2 shows the I-V curve of MSC360SMA120B under different driving voltages at  $T_j$  = 150°C. Note the small separation between the  $R_{DSon}$  curves at  $V_{GSon}$  = 20V and  $V_{GSon}$  = 18V, and compare this to the bigger differences in  $R_{DSon}$  as  $V_{GSon}$  drops increasingly below 16V. Some important considerations include:

- An over-current protection scheme based upon the maximum current may fail to trigger.

Designers should account for the higher variability of R<sub>DSon</sub> at lower V<sub>GSon</sub>.

- The small-signal transconductance, gm, is higher at lower V<sub>GSon</sub>. This effect can lead to switching instability, since V<sub>GS</sub> may be in a middle range in the presence of high drain-source voltage resulting in a short circuit event. (The peak short circuit current will be governed by the precise value and duration of V<sub>GSon</sub>. See the next subsection.)

#### SHORT CIRCUIT WITHSTAND TIME

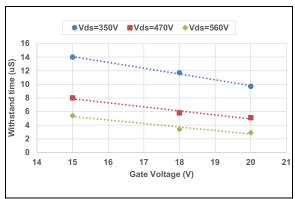

When driving with lower  $V_{GSon}$ , the maximum current will be lower under short circuit conditions, which can lead to a longer short circuit withstand time.

The following plot shows the short circuit withstand time (SCWT) in relation to gate and drain voltage for MSC035SMA070B measured with  $V_{DS}$  = 350V, 470V and 560V and  $V_{GSon}$  = 20V, 18V and 15V. It can be seen that the drain voltage is the most significant factor affecting SCWT, followed by  $V_{GS}$ .

**FIGURE 3:** Short Circuit Withstand Time of MSC035SMA070B.

In applications where short circuits may occur, the following considerations should be made:

- The SCWT specified in the data sheet is the typical time to failure, as defined by the device no longer exhibiting proper electrical function. In reality, the failure occurs after the device is switched off, when the latent heat generated causes irreversible damage. In essence, the delay does not happen when the measurement says it happens. Because of this delay, data sheet's SCWT can only be seen as a typical number.

- A more reasonable requirement would be that a specified number of devices are still operational after a specified number of short circuit events.

- Short circuit withstand time can be extended by increasing the device size or using multiple devices designed to drive at a reduced current level with source degeneration.

For additional guidance and insight, please contact your local Microchip sales team.

#### **Projected Lifetime**

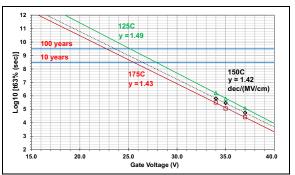

The below graph indicates that for every 2.5V increase in  $V_{GSon}$ , the projected lifetime of the gate oxide is reduced by an order of magnitude. This relationship applies over a wide range. It is a wear out mechanism due to accumulated damage over time.

**FIGURE 4:** Projected Device Lifetime Under Different Gate Voltage.

The lifetime of the gate oxide is mostly determined by the steady state gate ON drive voltage. The  $\pm 23V$  maximum rating on the gate is a recommendation for steady state gate voltage based on the projected lifetime of the device. Transient overshoots in  $V_{GSon}$  do not materially affect the device lifetime because of their brief duration. As an example, assume a rectangular overshoot for 20 ns at 25V with a nominal gate voltage of 20V. Per the oxide lifetime graph, the rate of degradation of the oxide during the pulse is 80 times higher. However, with a switching frequency of 100 kHz, the duty factor is 20/100,000 = 0.002. The relative stress, then, is only  $80 \times 0.002 = 16\%$ .

It should be noted that transient  $V_{GS}$  is not observable at the package pins. The gate and source lead inductances make it difficult to measure the actual gate voltage overshoot. Due to the high capacitance of the gate, the gate drive is normally over-dampened, and overshoot is rarely a problem. This is easiest to determine in simulations.

# Summary of V<sub>GSon</sub>

Microchip SiC MOSFETs can operate at +18V drive voltage with little loss in performance compared with the recommended +20V drive voltage. As can be seen in the above graphs, the increase in R<sub>DSon</sub> is much larger at 25°C than at 100°C-150°C. A system generally is penalized less by conduction loss than would be implied by the difference at 25°C if the die is hot. While the switching losses may be slightly higher under the same gate resistance, and saturation current will be lower, the positive trade-off is a longer short circuit withstand time.

Operation at  $V_{GSon}$  < 18V gate drive comes with elements of risk and should only be used if there is sufficient margin in  $R_{DSon}$ . Current sharing between paralleled devices can be problematic at colder junction temperatures. If  $V_{GSon}$  < 18V is needed, please contact your Microchip team for design support.

# OFF STATE DRIVING VOLTAGE, V<sub>GSoff</sub>

Microchip SiC MOSFETs are normally OFF power transistors. A negative  $V_{GSoff}$  is not required to keep the switch OFF during steady state. Rather, it is used to minimize switching loss and enhance switching stability.

- The presence of source inductance can slow the device turn-off process. A negative V<sub>GSoff</sub> is used to overcome this effect.

- A negative V<sub>GSoff</sub> provides more margin to avoid false turn on (also called shoot-through or cross conduction) during switching transients.

- A negative V<sub>GSoff</sub> has been used for decades with silicon IGBTs. Negative gate drive is not unique to SiC.

More complex modules with distributed transistors need a higher (more negative) V<sub>GSoff</sub> to avoid instability. Single transistor discrete designs can get by with very little negative V<sub>GSoff</sub>.

#### **Third Quadrant Conduction Performance**

Unlike a silicon IGBT, SiC MOSFETs can conduct current in both directions. The figure below shows the so-called "third quadrant" performance of Microchip's MSC360SMA120B; simply put, this is the drain current when the drain voltage is reversed. The body diode carries reverse drain current if the MOSFET's channel is turned OFF. In the case of  $V_{GSoff} = -5V$ , all current flows through the body diode. As  $V_{GS}$  is increased, the channel begins to form but maintains a substantial voltage drop even at  $V_{GS} = 0V$ , meaning the body diode still carries most of the reverse current. Following the switching transient, the channel can be turned ON to also conduct the reverse current to further improve conduction losses in a technique known as synchronous rectification.

**FIGURE 5:** Third Quadrant I-V Curve of MSC360SMA120B.

#### **BODY DIODE ROBUSTNESS**

There are no restrictions on use of the body diode in Microchip's SiC MOSFETs, but this is not true for all SiC MOSFET suppliers. Recent third-party measurements have shown that competitors' devices demonstrate body diode degradation to varying severity – in some cases, conduction losses increase by 20% after 168 hours; while in others, conduction losses more than double in less than 10 hours<sup>1</sup>. The degradation mechanism is called recombination-enhanced dislocation motion; the phenomena is well understood and has been observed in other semiconductors, such as SiGe, CdS, and GaAs. With certain device knowhow, the effects can be mitigated in SiC.

Again, it should be emphasized that customers can use Microchip's SiC MOSFET body diodes with confidence, but should you have any questions, please contact your local Microchip sales office.

## Switching Noise Immunity

There are important precautions to consider if using  $V_{GSoff}$  = 0V for SiC MOSFETs in high-speed, hard switching applications. Before diving into these precautions, some discussion about threshold voltage and pinch-off voltage is warranted.

Table 2 is from the data sheet of Microchip's 1200V, 80 mΩ SiC MOSFET in TO-247 package. Due to industry convention, the nominal threshold voltage  $V_{th}$  is measured under the conditions of  $V_{GS} = V_{DS}$ ,  $T_j = 25\,^{\circ}\text{C}$ , and a drain current of only 1 mA. Since the drain current associated with  $V_{th}$  is so low, the more relevant parameter to use for designs is known as the pinch-off voltage,  $V_p$ . The pinch-off voltage  $V_p$  is the value of  $V_{GS}$  that produces a given drain current at a specific  $V_{DS}$ .

Accordingly, the value of  $V_p$  has a dependence on VDS that varies by MOSFET architecture. Trench MOSFETs have a much higher variation in  $V_p$  than planar MOSFETs; for this reason, to help ensure safe operation, trench MOSFETs are designed such that  $V_{th}$  at 25°C is higher than needed. This means that planar MOSFETs offer greater design margin around  $V_p$ , which brings us at last to the key message on switching noise immunity.

The "real" margin for switching noise immunity should be set by  $V_p$  at the highest possible  $V_{DS}$  and the maximum allowed  $T_j$ . For our current generation SiC MOSFETs, Microchip guarantees turn-off with  $V_{GS} = 0V$  at  $T_j = 175^{\circ}\text{C}$ . Using a negative  $V_{GS\text{off}}$  provides more margin on  $V_p$ , which enhances switching stability and is the most certain way to prevent false turn-on.

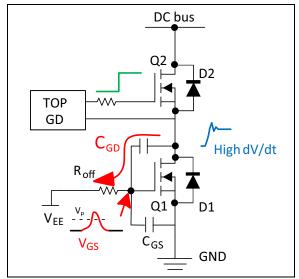

The false turn-on in a half bridge configuration is commonly induced by the miller capacitance (drain to gate capacitance  $C_{GD}$ ) as shown in Figure 6. When top device Q2 is turned ON the high midpoint (phase leg

output) dV/dt will induce current flow through  $C_{GD}$  that creates a voltage difference across gate resistor  $R_{OFF}$ . This voltage difference will make the actual gate voltage  $V_{GS}$  on bottom device Q1 higher than steady state OFF voltage  $V_{EE}$ . This voltage can be high enough to turn Q1 ON, the margin on  $V_p$  prevent this false turn-on.

FIGURE 6: Switching Induced False Turn ON in a Half Bridge Configuration.

### Summary of V<sub>GSoff</sub>

Due to the previous discussion, Microchip does not recommend the use of  $V_{GSoff} = 0V$ . For single-ended topologies with no danger of shoot-though (e.g., flyback, buck, or boost topologies), it is possible to use  $V_{GSoff} = 0V$ . Should  $V_{GSoff} = 0V$  be absolutely required, attention should be given to proper gate-source loop design. Specifically, designers should try to minimize three things: (i) parasitic drain-gate capacitance, (ii) gate-source loop inductance, and (iii) shared inductance between the gate-source loop and main current commutation loop.

TABLE 2: GATE-SOURCE THRESHOLD VOLTAGE OF MSC080SMA120B

| Symbol                   | Characteristics                       | Test Conditions                                 | Minimum | Typical | Maximum | Unit |

|--------------------------|---------------------------------------|-------------------------------------------------|---------|---------|---------|------|

| V <sub>GS(th),25°C</sub> | Gate-source threshold voltage at 25°C | $V_{GS} = V_{DS}$ , lo = 1 mA,<br>$T_j = 25$ °C | 1.8     | 2.8     |         | V    |

### **KEY TAKEAWAYS**

This application note provides guidance on Microchip SiC MOSFET gate-source voltage specifications and design considerations for making the most effective gate driver circuit. The following are key takeaways.

- For the best possible switching and conduction performance, Microchip recommends driving with V<sub>GSon</sub> = +20V and V<sub>GSoff</sub> = -5V.

- 2. It is permissible to deviate from these recommendations. Microchip SiC MOSFETs can operate at +18V with slight reductions in current capability and turn-on efficiency, but comes with the benefit of longer short circuit withstand time.

- 3. Driving current-generation Microchip SiC MOSFETs using  $V_{GSon} = 15V$  is not recommended. If this situation cannot be avoided, please contact Microchip for design assistance.

- 4. Microchip guarantees turn-off with  $V_{GS}$  = 0V at  $T_j$  = 175°C. That said, using a negative  $V_{GSoff}$  provides greater margin around  $V_p$ , which enhances switching stability and is the most certain way to prevent false turn-on.

#### **REFERENCE**

1. M. Kang *et al.*, "Body Diode Reliability of Commercial SiC Power MOSFETs", 2019 IEEE 7<sup>th</sup> Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2019, pp. 416-419.

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, Bes Time, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach. Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2022, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-0626-0

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

**Atlanta** Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4485-5910

Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

**Israel - Ra'anana** Tel: 972-9-744-7705

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40 Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820